Product Summary

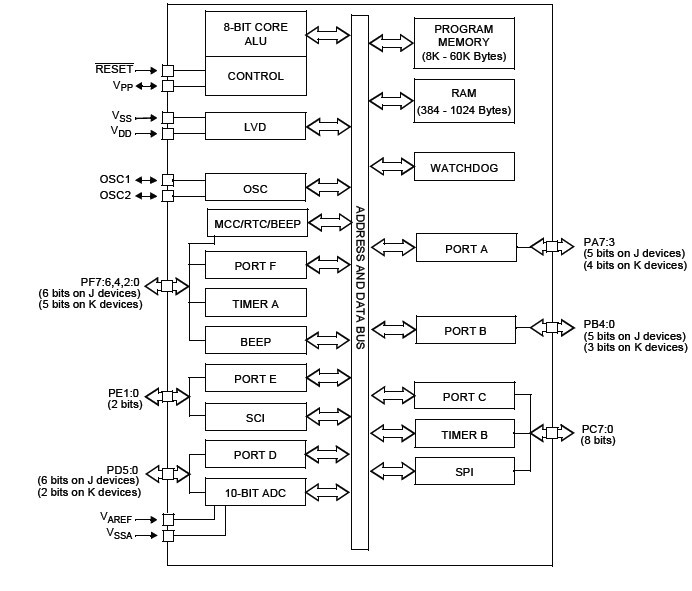

The ST72F324BJ2TAS device is a member of the ST7 microcontroller family designed for the 5V operating range. The ST72F324BJ2TAS is based on a common industrystandard 8-bit core, featuring an enhanced instruction set and are available with FLASH or ROM program memory.

Parametrics

ST72F324BJ2TAS absolute maximum ratings: (1)VDD - VSS Supply voltage: 6.5V; (2)VPP - VSS Programming Voltage 13; (3)VIN Input Voltage on true open drain pin: VSS-0.3 to 6.5V; (4)Input voltage on any other pin: VSS-0.3 to VDD+0.3; (5)|ΔVDDx| and |ΔVSSx| Variations between different digital power pins: 50 mV; (6)|VSSA - VSSx| Variations between digital and analog ground pins: 50mV.

Features

ST72F324BJ2TAS features: (1)8 to 32K dual voltage High Density Flash (HDFlash) or ROM with read-out protection capability. In-Application Programming and In-Circuit Programming for HDFlash devices; (2)384 to 1K bytes RAM; (3)HDFlash endurance: 100 cycles, data retention: 20 years at 55°C; (4)Enhanced low voltage supervisor (LVD) for main supply with programmable reset thresholds and auxiliary voltage detector (AVD) with interrupt capability; (5)Clock sources: crystal/ceramic resonator oscillators, internal RC oscillator, clock security system and bypass for external clock; (6)PLL for 2x frequency multiplication; (7)Four Power Saving Modes: Halt, Active-Halt, Wait and Slow; (8)8-bit Data Manipulation; (9)63 Basic Instructions; (10)17 main Addressing Modes; (11)8 x 8 Unsigned Multiply Instruction; (12)Full hardware/software development package; (13)In-Circuit Testing capability.

Diagrams

|

ST72101 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

ST72101G1 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

ST72104G |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

ST72104G1 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

ST72124J |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

ST72141 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))